Docket No.: 61282-060 PATENT

# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Application of

Customer Number: 20277

Sadami TAKEOKA, et al.

Confirmation Number: 2495

Application No.: 10/766,951

)/766.951

**Group Art Unit:**

Filed: January 30, 2004

Examiner:

For: A METHOD FOR EVALUATING DELAY TESTS QUALITY

# TRANSMITTAL OF CERTIFIED PRIORITY DOCUMENTS

Mail Stop CPD Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

Sir:

At the time the above application was filed, priority was claimed based on the following applications:

Japanese Patent Application JP 2003-021824, filed on January 30, 2003.

Japanese Patent Application JP 2004-018291, filed on January 27, 2004.

A copy of each priority application listed above is enclosed.

Respectfully submitted,

McDERMOTT WILL & EMERY LLP

Michael E. Fogarty

Registration No. 36,139

600 13th Street, N.W.

Washington, DC 20005-3096 Phone: 202.756.8000 MEF:blg Facsimile: 202.756.8087

Date: November 4, 2004

Please recognize our Customer No. 20277 as our correspondence address.

# 日本国特許庁 JAPAN PATENT OFFICE LEDermott Will & Emery LED

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed ith this Office.

出願年月日 Date of Application:

2003年 1月30日

出願番号 Application Number:

特願2003-021824

ST. 10/C]:

[JP2003-021824]

願 人 plicant(s):

松下電器産業株式会社

CERTIFIED COPY OF PRIORITY DOCUMENT

特許庁長官 Commissioner, Japan Patent Office 2004年 1月29日

【書類名】

特許願

【整理番号】

5037540158

【提出日】

平成15年 1月30日

【あて先】

特許庁長官殿

【国際特許分類】

G01R 31/28

【発明者】

【住所又は居所】

大阪府門真市大字門真1006番地 松下電器産業株式

会社内

【氏名】

竹岡 貞巳

【発明者】

【住所又は居所】

福岡県飯塚市伊岐須1-4-5-301

【氏名】

梶原 誠司

【特許出願人】

【識別番号】

000005821

【氏名又は名称】 松下電器産業株式会社

【代理人】

【識別番号】

100097445

【弁理士】

【氏名又は名称】 岩橋 文雄

【選任した代理人】

【識別番号】

100103355

【弁理士】

【氏名又は名称】

坂口 智康

【選任した代理人】

【識別番号】

100109667

【弁理士】

【氏名又は名称】 内藤 浩樹

【手数料の表示】

【予納台帳番号】 011305

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 9809938

# 【書類名】 明細書

【発明の名称】 遅延故障検査品質評価方法

【特許請求の範囲】

【請求項1】 半導体集積回路に対して遅延故障を定義する遅延故障定義手段と、前記遅延故障定義手段によって定義された遅延故障のうちの一部の遅延故障を選択する遅延故障選択手段と、前記遅延故障選択手段で選択されたおのおのの遅延故障に対してテスト可能か否かを判定する第1のテスト可否判定手段と、前記テスト可否判定手段でテスト不能と判定された遅延故障の数を用いて遅延故障検出率を算出する遅延故障検出率算出手段を備える遅延故障検査品質評価方法。

【請求項2】 前記遅延故障定義手段では、前記半導体集積回路中のすべての信号経路についてパス遅延故障を定義することを特徴とする請求項1の遅延故障検査品質評価方法。

【請求項3】 前記遅延故障定義手段では、前記半導体集積回路中のすべての ノードに対して遅延故障を定義することを特徴とする請求項1の遅延故障検査品 質評価方法。

【請求項4】 前記遅延故障定義手段ではさらに、前記半導体集積回路中の遅延故障について、あらかじめテスト可能か否かを判定する第2のテスト可否判定手段を備え、前記第2のテスト可否判定手段によってテスト可能と判定された遅延故障のみを前記半導体集積回路に定義することを特徴とする請求項1の遅延故障検査品質評価方法。

【請求項5】 前記遅延故障定義手段では、全遅延故障数よりも小さい所定数の遅延故障を前記半導体集積回路に定義することを特徴とする請求項1の遅延故障検査品質評価方法。

【請求項6】 前記遅延故障選択手段では、前記遅延故障定義手段で定義された遅延故障のうち、所定数もしくは所定割合の遅延故障をランダムに選択することを特徴とする請求項1の遅延故障検査品質評価方法。

【請求項7】 前記遅延故障選択手段では、前記遅延故障定義手段で定義されたパス遅延故障のうち、各ノードについて前記ノードを通る最大遅延値の信号経路を選択することを特徴とする請求項2の遅延故障検査品質評価方法。

【請求項8】 前記遅延故障選択手段では、前記遅延故障定義手段で定義されたパス遅延故障のうち、各ノードについて前記ノードを通る最大ゲート段数の信号経路を選択することを特徴とする請求項2の遅延故障検査品質評価方法。

【請求項9】 前記遅延故障選択手段では、前記遅延故障定義手段で定義されたパス遅延故障のうち、各ノードについて前記ノードを通る最長の信号経路を選択することを特徴とする請求項2の遅延故障検査品質評価方法。

【請求項10】 前記第1のテスト可否判定手段では、前記遅延故障選択手段で選択された遅延故障に対して検査系列生成を行い、検査系列生成不能である遅延故障をテスト不能と判定することを特徴とする請求項1の遅延故障検査品質評価方法。

【請求項11】 前記遅延故障検出率算出手段ではさらに、前記遅延故障定義手段で定義された遅延故障に対して、与えられた検査系列を用いて遅延故障シミュレーションを実行する遅延故障シミュレーション手段と、前記遅延故障定義手段で定義された遅延故障数と、前記第1のテスト可否判定手段で判定されたテスト不能な遅延故障数と、前記遅延故障シミュレーションによって検出された遅延故障数とを用いて故障検出率計算を行う故障検出率計算手段とを備えることを特徴とする請求項1の遅延故障検査品質評価方法。

【請求項12】 前記故障検出率計算手段では、前記第1のテスト可否判定手段で判定されたテスト不能な遅延故障数に対して、前記遅延故障選択手段で選択された遅延故障数と前記遅延故障定義手段で定義された遅延故障数との比を積算した値を全テスト不能故障数とし、遅延故障検出率の分子を前記遅延故障シミュレーション手段で検出された遅延故障数とし、遅延故障検出率の分母を前記遅延故障選択手段で選択された遅延故障数から前記全テスト不能故障数の減算で計算を行うことを特徴とする請求項11の遅延故障検査品質評価方法。

【請求項13】 前記遅延故障定義手段ではさらに、パス遅延故障が定義された信号経路の設計上の遅延量の合計値を算出する第1の合計値算出手段を備え、前記第1のテスト可否判定手段ではさらに、テスト不能と判定されたパス遅延故障の信号経路の設計上の遅延量の合計値を算出する第2の合計値算出手段を備え、前記遅延故障検出率算出手段にはさらに、検出されたパス遅延故障の信号経路

の設計上の遅延量の合計値を算出する第3の合計値算出手段と、前記第1の合計 値算出手段で算出された定義されたパス遅延故障の信号経路の設計上の遅延量の 合計値と、前記第2の合計値算出手段で算出されたテスト不能なパス遅延故障の 信号経路の設計上の遅延量の合計値と、前記第3の合計値算出手段で算出された 検出されたパス遅延故障の信号経路の設計上の遅延量の合計値とを用いて故障検 出率計算を行う故障検出率計算手段とを備えることを特徴とする請求項2の遅延 故障検査品質評価方法。

【請求項14】 前記故障検出率計算手段では、前記第2の合計値算出手段で 算出されたテスト不能なパス遅延故障の信号経路の設計上の遅延量の合計値に対 して、前記遅延故障選択手段で選択された遅延故障数と前記遅延故障定義手段で 定義された遅延故障数との比を積算した値を全テスト不能故障量とし、遅延故障 検出率の分子を前記第3の合計値算出手段で算出された検出されたパス遅延故障 の信号経路の設計上の遅延量の合計値またはその100倍の値とし、遅延故障検 出率の分母を前記第1の合計値算出手段で算出された定義されたパス遅延故障の 信号経路の設計上の遅延量の合計値から前記全テスト不能故障量の減算で計算を 行うことを特徴とする請求項13の遅延故障検査品質評価方法。

【請求項15】 前記信号経路の設計上の遅延量は設計上の信号経路の設計上の遅延値を用いることを特徴とする請求項13、および14の遅延故障検査品質評価方法。

【請求項16】 前記信号経路の設計上の遅延量は信号経路上のゲート段数を 用いることを特徴とする請求項13、および14の遅延故障検査品質評価方法。

【請求項17】 前記信号経路の設計上の遅延量は物理的な信号経路長を用いることを特徴とする請求項13、および14の遅延故障検査品質評価方法。

### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、半導体集積回路の遅延故障検査を行う際に使用する検査系列の故障 検査能力を表す品質の評価に関するものである。

$[0\ 0\ 0\ 2]$

# 【従来の技術】

近年の半導体プロセスの微細化技術の急速な進歩によって、半導体集積回路の 大規模化、複雑化が急激に進み、これに伴って半導体集積回路の検査がいっそう 困難になっている。この問題に対処するため、半導体集積回路の検査を容易化す る手段としてスキャン方式などによる検査容易化設計手法が普及し、縮退故障モ デルで表される故障は効率的に検査できるようになった。縮退故障モデルで仮定 された故障を検出する場合、故障検出の能力はクロック周波数に依存しないため 、従来スキャンテストを実施する際には、一般的に実動作速度よりも低いクロッ ク周波数を使って行われてきた。しかし、半導体プロセスの微細化の進行と共に 、プロセスのばらつきが顕在化し、従来のスキャン方式を使った低いクロック周 波数による検査だけでは十分に検査品質を保証することができなくなり、実動作 時と同じクロック周波数を使った遅延故障検査技術のような、遅延を考慮した検 査が必要とされるようになった。従来の遅延故障検査技術は特許文献1などに開 示されている。

[0003]

#### 【特許文献 1】

特開平9-269959号公報

[0004]

#### 【発明が解決しようとする課題】

遅延故障用の検査系列の品質を表す故障検出率は一般には次のような式で表わ すのがよいと考えられている。

[0005]

故障検出率=検出故障数/(全定義故障数-テスト不能故障数)

しかしながら、(式1)におけるテスト不能故障数を正確に算出することは膨大な計算時間と計算機メモリを要するため非現実的であった。このため、従来は 故障検出率を次のような式で代用するのが一般的であった。

[0006]

故障検出率=検出故障数/全定義故障数×100(%) (式2)

しかしながら、特にパス遅延故障の場合、縮退故障と異なりテスト不能故障の 割合が非常に大きいことが知られており、(式2)のようにテスト不能故障を考 慮しない故障検出率算出方法では、テスト可能な故障をすべて検出しているにも 係わらず故障検出率が非常に低い値となってしまう場合があり、算出された数値 が実際のテスト品質を正しく評価できないという問題があった。

# [0007]

さらには、仮に(式1)を用いることができた場合でも、どの遅延故障も重要度が等しいと見なされるため、(式1)の故障検出率は検査系列の実際の故障検査に対する品質を十分に反映できていない、という問題をはらんでいた。この問題を図を用いて具体的に説明する。

# [0008]

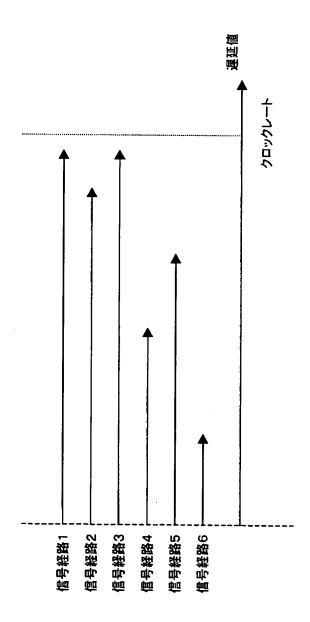

図11は、半導体集積回路上に定義した遅延故障の特性を示すための図である。信号経路1~6の右側に示した矢印の長さは、それぞれ各信号経路の設計上の遅延値を示す。また図の右側の点線は半導体集積回路の1クロックレートの値を表す。なお、説明の便宜上、信号経路1~6はすべてテスト可能として説明を行う。

#### [0009]

一般に、信号経路の設計上の遅延値が大きいほど(1クロックレートに近いほど)、この信号経路が遅延故障を生じる可能性が大きい。したがって、図11において、信号経路3が信号経路6よりも遅延故障を生じる可能性が大きいことは明らかである。そのため信号経路3に定義した遅延故障を検出する検査は、信号経路6に定義した遅延故障を検出する検査よりも検査の品質がより高いと言える。しかしながら、従来用いていた故障検出率では、信号経路3上の遅延故障を検出した場合も、信号経路6上の遅延故障を検出した場合も、同じく1個の遅延故障を検出したと扱われ、その品質は同等とみなされる。例えば、信号経路1~6上にそれぞれ1個ずつ遅延故障を定義したと仮定すると、信号経路1~3上の故障を検出した場合も、信号経路4~6上の故障を検出した場合も、故障検出率はいずれも等しく、3/6×100[%]=50%となる。

# [0010]

遅延値の大きな信号経路1~3上を故障検出する検査と、遅延値の小さな信号 経路4~6を故障検査する検査とでは、前者の方が品質が高いのは明らかである ので、したがって従来の検査で使用していた故障検出率(式1)は、検査の品質 を正しく表しておらず、そのため検査に使用する検査系列の品質を誤って評価し てしまっていた、という問題があった。

# $[0\ 0\ 1\ 1]$

本発明はこのような問題を解決するために、遅延故障用の検査系列の品質を評価する際に、テスト不能な遅延故障数を推定することによって、(式1)を現実的に実施可能とすることを第1の目的とし、さらには遅延故障を定義した信号経路上の設計上の遅延値を考慮することによって、遅延故障検査系列の品質をより高精度に評価することのできる遅延故障検査品質評価方法を提供することを第2の目的とする。

# $[0\ 0\ 1\ 2]$

# 【課題を解決するための手段】

以上の目的を達成するため、本発明に係る遅延故障検査系列の品質評価方法は、半導体集積回路に対して遅延故障を定義する遅延故障定義手段と、定義された遅延故障のうちの一部の遅延故障を選択する遅延故障選択手段と、選択されたおのおのの遅延故障に対してテスト可能か否かを判定する第1のテスト可否判定手段と、選択された故障のうちテスト不能と判定された遅延故障の数を用いて遅延故障検出率を算出する遅延故障検出率算出手段を備える。

#### [0013]

また、前記遅延故障定義手段ではさらに、各遅延故障について、あらかじめテスト可能か否かを判定する第2のテスト可否判定手段を備え、ここでテスト可能と判定された遅延故障のみを前記半導体集積回路に定義する。または、前記遅延故障定義手段では、全遅延故障数よりも小さい所定数の遅延故障を前記半導体集積回路に定義する。

#### $[0\ 0\ 1\ 4]$

また、前記遅延故障選択手段では、定義された遅延故障のうち、所定数もしくは所定割合の遅延故障をランダムに選択する。

# [0015]

または、前記遅延故障選択手段では、定義されたパス遅延故障のうち、各ノードについて前記ノードを通る最大遅延値の信号経路を選択する。

# [0016]

または、前記遅延故障選択手段では、定義されたパス遅延故障のうち、各ノードについて前記ノードを通る最大ゲート段数の信号経路を選択する。

#### $[0\ 0\ 1\ 7]$

または、前記遅延故障選択手段では、定義されたパス遅延故障のうち、各ノードについて前記ノードを通る最長の信号経路を選択する。

# [0018]

また、前記第1のテスト可否判定手段では、選択された遅延故障に対して検査 系列生成を行い、検査系列生成不能である遅延故障をテスト不能と判定する。

# [0019]

また、前記遅延故障検出率算出手段ではさらに、定義された遅延故障に対して、与えられた検査系列を用いて遅延故障シミュレーションを実行する遅延故障シミュレーション手段と、定義された遅延故障数と、前記第1のテスト可否判定手段で判定されたテスト不能な遅延故障数と、前記遅延故障シミュレーションによって検出された遅延故障数とを用いて故障検出率計算を行う故障検出率計算手段とを備える。

# [0020]

または、前記故障検出率計算手段では、前記第1のテスト可否判定手段で判定されたテスト不能な遅延故障数に対して、選択された遅延故障数と定義された遅延故障数との比を積算した値を全テスト不能故障数とし、遅延故障検出率の分子を前記遅延故障シミュレーション手段で検出された遅延故障数またはその100倍の値とし、遅延故障検出率の分母を選択された遅延故障数から全テスト不能故障数の減算で計算を行う。

# [0021]

また、前記遅延故障定義手段ではさらに、パス遅延故障が定義された信号経路の設計上の遅延量の合計値を算出する第1の合計値算出手段を備え、前記第1の

テスト可否判定手段ではさらに、テスト不能と判定されたパス遅延故障の信号経路の設計上の遅延量の合計値を算出する第2の合計値算出手段を備え、前記遅延故障検出率算出手段にはさらに、検出されたパス遅延故障の信号経路の設計上の遅延量の合計値を算出する第3の合計値算出手段と、前記第1の合計値算出手段で算出された定義されたパス遅延故障の信号経路の設計上の遅延量の合計値と、前記第2の合計値算出手段で算出されたテスト不能なパス遅延故障の信号経路の設計上の遅延量の合計値と、前記第3の合計値算出手段で算出された検出されたパス遅延故障の信号経路の設計上の遅延量の合計値とを用いて故障検出率計算を行う故障検出率計算手段とを備える。

#### $[0\ 0\ 2\ 2]$

また、前記故障検出率計算手段では、前記第2の合計値算出手段で算出された テスト不能なパス遅延故障の信号経路の設計上の遅延量の合計値に対して、前記 遅延故障選択手段で選択された遅延故障数と前記遅延故障定義手段で定義された 遅延故障数との比を積算した値を全テスト不能故障量とし、遅延故障検出率の分 子を前記第3の合計値算出手段で算出された検出されたパス遅延故障の信号経路 の設計上の遅延量の合計値またはその100倍の値とし、遅延故障検出率の分母 を前記第1の合計値算出手段で算出された定義されたパス遅延故障の信号経路の 設計上の遅延量の合計値から前記全テスト不能故障量の減算で計算を行う。

#### [0023]

また、前記信号経路の設計上の遅延量は設計上の信号経路の設計上の遅延値、もしくは信号経路上のゲート段数、もしくは物理的な信号経路長を用いる。

#### [0024]

#### 【発明の実施の形態】

一般に1つのノード上または信号経路上の遅延故障には、立上がり遷移の故障と立下り遷移の故障の2種類があり、遅延故障はノードまたは信号経路と遷移の種類との組合せで表される。しかし本明細書中では以後、説明の便宜上、遷移の種類は省略して1つのノードまたは信号経路上には1つの遅延故障が定義されるものとして説明を行う。

### [0025]

# (第1の実施の形態)

本実施の形態は、定義された遅延故障のうちのテスト不能な遅延故障数を推定することによって、遅延故障検査系列の品質評価の精度を向上させる具体的な実施方法について説明したものである。

#### [0026]

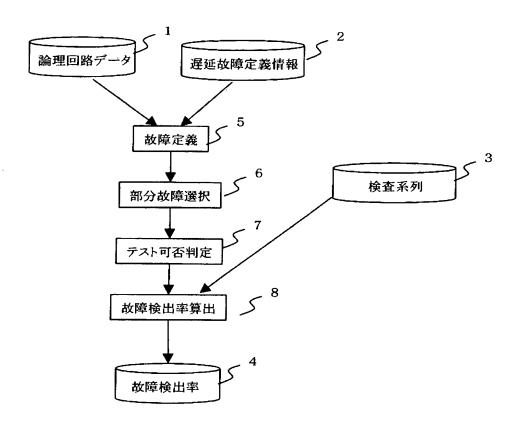

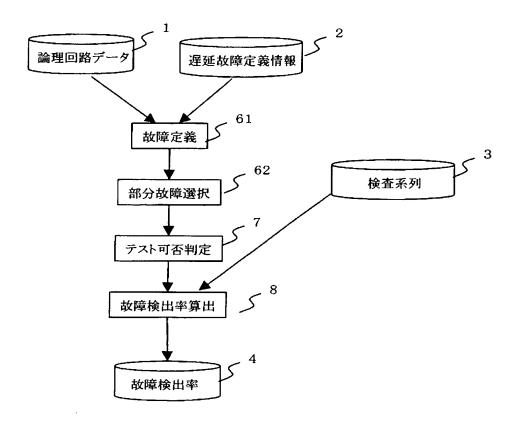

図1は本発明に係わる遅延故障検査品質評価方法を示すフローチャートである。1は検査対象である論理回路データ、2は論理回路中に定義する遅延故障定義情報、3は遅延故障検査に用いる検査系列、4は故障検出率、5は論理回路に対して遅延故障を定義する故障定義操作、6は定義された故障のうちの一部を選択する部分故障選択操作、7は選択された故障がテスト可能か否かを判定するテスト可否判定操作、8は故障検出率を算出する故障検出率算出操作を示す。なお、遅延故障定義情報2には、定義する故障のリスト、または全故障を定義する旨の指示、または論理回路中の一部のブロックに対してのみ故障を定義する旨の指示、のように論理回路中へ故障を定義するために必要な情報が格納されているものとする。

# [0027]

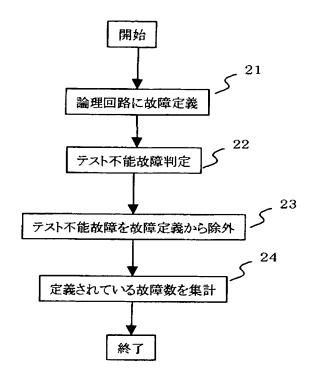

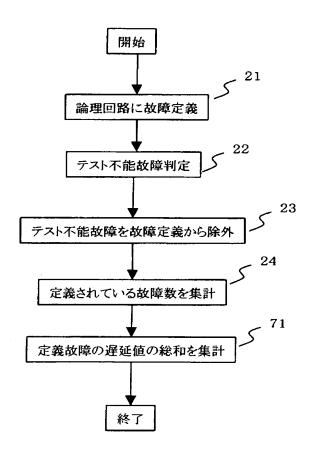

図2は操作5の故障定義操作のより詳細を示すフローチャートである。21は 論理回路に対して故障を定義する操作、22は定義された故障に対して、前処理 として容易にテスト不能と判別できる故障を判別するテスト不能故障判定操作、 23は操作22でテスト不能と判定された故障を故障定義から除外する操作、2 4は操作23の結果、除外されずに定義されている故障数を集計する操作を示す

### [0028]

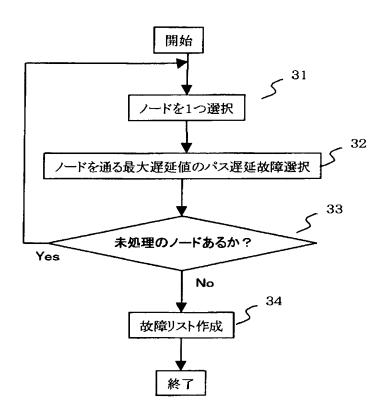

図3は操作6の部分故障選択操作のより詳細を示すフローチャートである。3 1は回路中のノードを1つ選択する操作、32は選択したノードを通る最大遅延 値のパス遅延故障を選択する操作、33は未処理ノードの有無の判定、34は操 作32で選択された信号経路を集計する操作を示す。なお、操作32では、最大 遅延値の信号経路が複数あった場合には、すべて選択するものとする。

#### [0029]

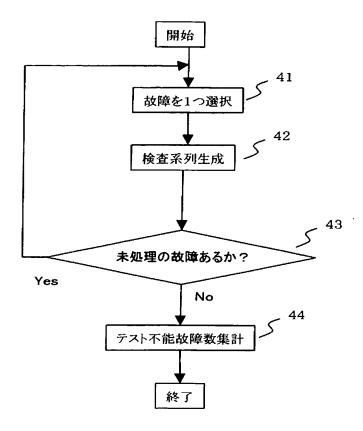

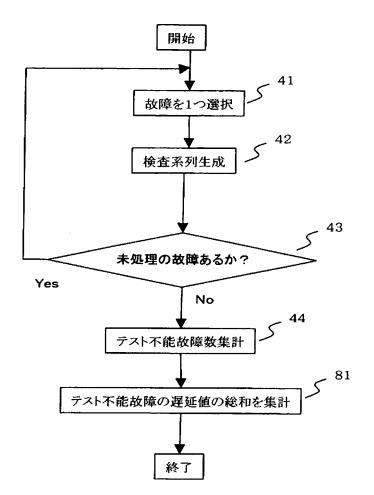

図4は操作7のテスト可否判定操作のより詳細を示すフローチャートである。 41は遅延故障を1つ選択する操作、42は選択した遅延故障に対して検査系列を生成する操作、43は未処理の故障があるか否かの判定、44は操作42においてテスト不能と判明した故障数を集計する操作を示す。なお、操作42における検査系列生成方法は、本実施形態では従来から用いられている一般的な方法を用いるものとして、その詳細説明は省略する。

# [0030]

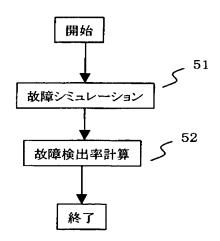

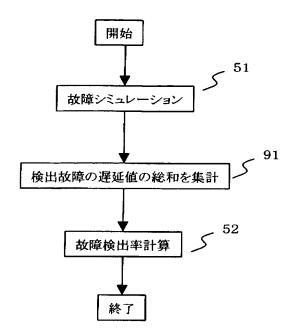

図5は操作8の故障検出率算出操作のより詳細を示すフローチャートである。 51は故障シミュレーションを実行する操作、52は故障検出率を計算する故障 検出率計算操作を示す。

#### [0031]

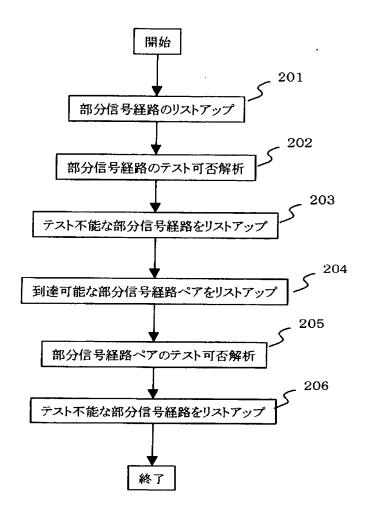

図12は操作22のより詳細を示すフローチャートである。操作22は本実施 形態では一般に用いられている既知の方法(例えば「電子情報通信学会論文誌 D ー I Vol. J82ーDーI No. 7 pp. 888-896」)を用いるものとして説明する。201は部分信号経路をリストアップする操作、202は 各部分信号経路についてテスト可能か否かを解析する操作、203はテスト不能 な部分信号経路を通るパス遅延故障をすべてテスト不能故障としてリストアップ する操作、204は到達可能な部分信号経路ペアをリストアップする操作、205は部分信号経路ペアがテスト可能か否かを解析する操作、206は操作204でテスト不能と判定された部分信号経路ペアを通るパス遅延故障をテスト不能故障としてリストアップする操作を示す。

#### [0032]

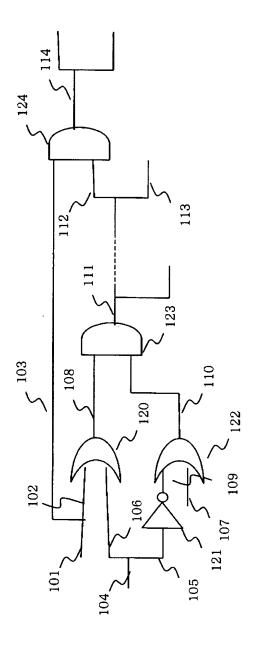

図13は本実施の形態を説明する回路図である。101~114は信号線、120はORゲート、121、122はインバータ、123、124はANDゲートを示す。

#### [0033]

以下、図 $1\sim5$ 、および図12、13を用いて本発明の第1の実施の形態を説明する。

#### [0034]

本実施形態では、遅延故障の一例としてパス遅延故障を用いて説明を行う。

#### [0035]

初めに与えられた論理回路データ1に対して遅延故障定義情報2を用いて故障 定義操作5を行う。遅延故障定義情報2は本実施の形態においては、全故障定義 の指示が格納されているものとして説明を行う。次に故障定義操作5では、まず 操作21において、遅延故障定義情報2の指示に基づいて論理回路中のすべての 信号経路についてパス遅延故障を定義する。ここで定義されたパス遅延故障数と その中に含まれるテスト不能故障数はそれぞれ15000個、2200個である と仮定する。

# [0036]

次に操作22では、定義した全パス遅延故障に対して簡易的なテスト不能パス 判定を行う。まず操作201において部分信号経路のリストアップを行う。ここ で部分信号経路とは、外部入力(外部双方向を含む)または分岐の枝を始点とし 、外部出力(外部双方向を含む)または分岐の幹を終点とする信号経路とする。 図13において、例えば信号線102、103、105、106が分岐の枝であ り、また信号線101、104、111、114が分岐の幹であるので、操作2 01では、経路(信号線103→信号線113)、経路(信号線102→信号線 108→信号線111)、経路(信号線106→信号線108→信号線111) 、経路(信号線105→信号線109→信号線110→信号線111)、経路( 信号線112→信号線114)の5つが部分信号経路としてリストアップされる 。続いて操作202では5つの部分信号経路についてテスト可能か否かの解析を 行う。ここでは、おのおのの部分信号経路について遷移が伝搬する操作を試み、 成功すればテスト可能、矛盾が生じればテスト不能と判定する。例えば、経路( 信号線106→信号線108→信号線111)においては、信号線101、10 7の値をそれぞれ0、1に固定することが可能であれば、経路の活性化が可能で あるためテスト可能と判定される。今操作202では、経路(信号線105→信 号線109→信号線110→信号線111)のみが、信号線107が必ず1に固 定されてしまうためテスト不能と判定されたとし、他の部分信号経路はすべてテ スト可能と判定されたとする。次に操作203では、テスト不能な部分信号経路

である経路(信号線105→信号線109→信号線110→信号線111)上を 通るパス遅延故障をすべてテスト不能故障としてリストアップする。ここでは2 000個の故障がリストアップされたものとする。引き続いて操作204では、 テスト不能な部分信号経路を除外して、到達可能な部分信号経路のペアをすべて リストアップする。例えば経路(信号線102→信号線108→信号線111) から経路(信号線112→信号線114)へは到達可能であり、この2つの部分 信号経路のペアを{経路(信号線102→信号線108→信号線111),経路 (信号線112→信号線114)↓ と表記することとすると、2つの部分信号経 路のペア 「経路(信号線102→信号線108→信号線111), 経路(信号線 1),経路(信号線112→信号線114)∤がリストアップされる。さらに操 作205では、おのおのの部分信号経路のペアがテスト可能か否かを判定する。 例えば{経路(信号線106→信号線108→信号線111). 経路(信号線1 1 2 →信号線 1 1 4 ) ↓ においては、経路(信号線 1 0 6 →信号線 1 0 8 →信号 線111)の遷移伝搬のためには信号線102の値が0であることが必要である が、一方、経路(信号線106→信号線108→信号線111)の遷移伝搬のた めには信号線103の値が1であることが必要であり、両者が矛盾する。したが 2→信号線114) はテスト不能と判定される。一方 |経路(信号線102→ 信号線108→信号線111),経路(信号線112→信号線114) は矛盾 が生じず、テスト可能と判定されたものとする。最後に操作206では、 |経路 (信号線106→信号線108→信号線111)、経路(信号線112→信号線 114)~ を通るパス遅延故障がすべてテスト不能故障としてリストアップされ る。ここでは3000個の故障がリストアップされたものとする。

# [0037]

したがって操作22では合計5000個のパス遅延故障がテスト不能と判定される。引き続き操作23ではテスト不能と判定された5000個のパス遅延故障を定義から除外する。さらに操作24では、定義されている故障数が(15000個-5000個)により10000個と集計される。

# [0038]

次に部分故障選択操作6では、まず操作31でノードを1つ選択する。なお、 与えられた論理回路データ1中には3000のノードが存在するものとする。次 に操作32では選択したノードを通る定義されたパス遅延故障のうち、信号経路 上の遅延値が最も大きいパス遅延故障を選択する。もし選択したノードを诵る定 義されたパス遅延故障が存在しない場合は、そのノードは処理済みとして、操作 33へ進む。今、選択されたパス遅延故障上に10個のノードが含まれたとする 。引き続いて操作33では、未処理のノードがあるか否かの判定を行い、299 0個のノードが未処理なので、再度操作31へ進み、未処理のノードを1つ選択 し、操作32へ進んで選択したノードを通る信号経路上の遅延値が最も大きいパ ス遅延故障を選択する。今、選択されたパス遅延故障上に20個のノードが含ま れたとする。引き続いて操作33では、未処理のノードがあるか否かの判定を行 い、2970個のノードが未処理なので、再度操作31へ進む。同様に操作31 から操作33の繰り返しを行い、判定33において未処理のノードが存在しなく なったら、最後に操作34において、これまで操作32で選択されたパス遅延故 障を集計して故障リストを作成する。今、1000個のパス遅延故障による故障 リストが作成されたものとする。

### [0039]

次にテスト可否判定操作7では、まず操作41において、操作34で作成された故障リスト中のパス遅延故障を1つ選択する。次に操作42では、選択した故障に対する検査系列生成操作を行い、テスト可能かテスト不能かの判定を行う。引き続き操作43では、未処理の故障があるかどうかを判定する。ここではまだ999個の故障が残っているので、再度操作41へ進み、新たにパス遅延故障を1つ選択する。次に操作42では、選択した故障に対する検査系列生成操作を行い、テスト可能かテスト不能かの判定を行う。引き続き操作43では、未処理の故障があるかどうかの判定が、まだ998個の故障が残っているので、再度操作41へ進む。同様に操作41から操作43を繰り返し、操作43において未処理の故障がなくなったら、最後に操作44において、操作42でテスト不能と判定された故障の数を集計する。今、操作42でテスト不能と判定された故障の数を集計する。今、操作42でテスト不能と判定された故障数が2

00個であったとする。

# [0040]

次に故障検出率算出操作8では、まず操作51において、与えられた検査系列3を用いて故障シミュレーションを実施する。このとき対象となる故障は操作24で集計されたすべての故障である。この操作で検出された故障数が6000個であったとする。次に操作52では、操作51で検出された故障数を検出故障数とし、操作24で集計された定義故障数を全定義故障数とし、操作34で作成された故障リスト中の故障数を部分選択故障数とし、操作44で集計されたテスト不能故障数を部分テスト不能故障数として、次の式によって全定義故障中のテスト不能故障数を算出する。

#### [0041]

テスト不能故障推定数=部分テスト不能故障数

次に算出されたテスト不能故障推定数を用いて、次の式によって故障検出率を 算出する。

#### [0042]

故障検出率=検出故障数/(全定義故障数-テスト不能故障推定数)

今、部分テスト不能故障数、全定義故障数、部分選択故障数、検出故障数は、 それぞれ200個、10000個、1000個、6000個であるので、(式3 )よりテスト不能故障推定数は2000個と算出され、次に(式4)によって、 故障検出率は75%と算出される。

#### [0043]

一方、実際のテスト不能故障数は2200個なので、(非現実的な時間を要するが)実際の故障検出率を算出すると(式1)より76.9%となる。

#### [0044]

これに対して従来代用されていた(式 2 )による故障検出率ではテスト不能故障の数を全く考慮しないために 6 0 %という非常に低い値となってしまい、与えられた検査系列による検査品質を過小に見積もってしまう結果となる。

# [0045]

実際の実験結果の一例として、ISCAS89ベンチマーク回路の1つである s38417への実行結果から、従来代用されていた故障検出率(式2)が80%となる検査系列を用いて、テスト可能な実際の故障検出率(式1)、本実施形態の手法による故障検出率(式4)を求めると、それぞれ85.6%、85.7%であり、本実施形態の手法が非常に精度が高いことがわかる。

#### [0046]

以上から、本発明による遅延故障検査品質評価方法では、テスト不能故障と推 定される故障の数を考慮することによって、実際の故障検出率に近い故障検出率 の値を算出することができる。

# [0047]

なお、部分故障選択操作6の実行方法として本実施の形態で説明に使用した図3の方法の代わりに、操作24で定義されている故障からランダムで所定数の故障を選択しても同様の効果が得られることは明らかである。

# [0048]

また操作32において、本実施の形態ではノードを通る最大遅延値のパス遅延 故障を選択する、として説明を行ったが、最大遅延値の代わりに最大ゲート段数 か、または物理的な最大信号経路長を用いても同様の効果を得ることができる。 なお、上記物理的な信号経路長はレイアウトデータから算出できる信号経路上の 配線長の総和を用いてもよい。

#### [0049]

さらには、遅延故障定義情報2の内容は、本実施の形態では、全故障を定義するための指示、として説明を行ったが、全故障の一部で構成される故障リスト、または論理回路データ1の1ブロックに対して故障を定義するための指示などのように、全故障ではなく一部の故障を定義するものであっても同様の効果を得ることができる。

#### [0050]

(第2の実施の形態)

本実施の形態は、定義された遅延故障のうちのテスト不能な遅延故障数を推定

することによって、遅延故障検査系列の品質評価の精度を向上させる第1の実施 の形態とは別の実施方法について説明したものである。

# [0051]

本実施の形態では、遅延故障の別の例としてノード上の遅延故障を用いて説明を行う。ノード上の遅延故障を本実施の形態においては、遷移故障と呼ぶこととする。

# [0052]

図6は本発明に係わる遅延故障検査品質評価方法を示すフローチャートである。61は論理回路中の各ノードに対して故障定義を行う故障定義操作、62は定義された故障のうち所定数または所定割合の故障をランダムで選択する操作を示し、その他の記号は図1に一致する記号と同じものを表す。

#### [0053]

以下、図6、図4、および図5を用いて本発明の第2の実施の形態を説明する。

# [0054]

初めに与えられた論理回路データ1に対して遅延故障定義情報2を用いて故障定義操作61を行う。遅延故障定義情報2は本実施の形態においては、全故障定義の指示が格納されているものとして説明を行う。次に故障定義操作61では、与えられた論理回路データ1の全ノードへ遷移故障を定義する。なお、与えられた論理回路データ1中には3000のノードが存在するものとすると、全定義故障数は3000個となる。このとき、3000個の故障に含まれるテスト不能故障数は520個であると仮定する。

#### [0055]

次に部分故障選択操作62では、全定義故障のうちの所定数または所定割合の 故障をランダムで選択する。ここでは所定割合10%の故障を選択するものとす ると、操作62でランダムに選択される故障数は300となる。

#### [0056]

次にテスト可否判定操作7では、まず操作41において、操作62で選択された300個の遷移故障のうちから、故障を1つ選択する。次に操作42では、選

択した故障に対する検査系列生成操作を行い、テスト可能かテスト不能かの判定を行う。引き続き操作43では、未処理の故障があるかどうかを判定する。ここではまだ299個の故障が残っているので、再度操作41へ進み、新たに遷移故障を1つ選択する。次に操作42では、選択した故障に対する検査系列生成操作を行い、テスト可能かテスト不能かの判定を行う。引き続き操作43では、未処理の故障があるかどうかの判定が、まだ298個の故障が残っているので、再度操作41へ進む。同様に操作41から操作43を繰り返し、操作43において未処理の故障がなくなったら、最後に操作44において、操作42でテスト不能と判定された故障の数を集計する。今、操作42でテスト不能と判定された故障の数を集計する。

# [0057]

次に故障検出率算出操作8では、まず操作51において、与えられた検査系列3を用いて故障シミュレーションを実施する。このとき対象となる故障は操作61で定義されたすべての故障である。この操作で検出された故障数が2000個であったとする。次に操作52では、操作51で検出された故障数を検出故障数とし、操作61で定義された定義故障数を全定義故障数とし、操作62で選択された故障数を部分選択故障数とし、操作44で集計されたテスト不能故障数を部分テスト不能故障数として、(式3)によって全定義故障中のテスト不能故障推定数を算出する。次に算出されたテスト不能故障推定数を用いて、(式4)によって故障検出率を算出する。

#### [0058]

今、部分テスト不能故障数、全定義故障数、部分選択故障数、検出故障数は、それぞれ50個、3000個、300個、2000個であるので、(式3)よりテスト不能故障推定数は500個と算出され、次に(式4)によって、故障検出率は80%と算出される。

# [0059]

一方、実際のテスト不能故障数は520個なので、実際の故障検出率を算出すると(式1)より80.6%となる。

### [0060]

これに対して従来代用されていた(式2)による故障検出率ではテスト不能故障の数を全く考慮しないために66.7%という非常に低い値となってしまい、与えられた検査系列による検査品質を過小に見積もってしまう結果となる。

# [0061]

なお、遅延故障定義情報2の内容は、本実施の形態では、全故障を定義するための指示、として説明を行ったが、全故障の一部で構成される故障リスト、または論理回路データ1の1ブロックに対して故障を定義するための指示などのように、全故障ではなく一部の故障を定義するものであっても同様の効果を得ることができる。

#### [0062]

(第3の実施の形態)

本実施の形態は、遅延故障を定義した信号経路上の設計上の遅延値を用いて、 遅延故障検査系列の品質評価を行うことによって、遅延故障検査系列の品質評価 の精度を向上させる具体的な実施方法について説明したものである。

# [0063]

本実施形態では、遅延故障の一例としてパス遅延故障を用いて説明を行う。

#### $[0\ 0\ 6\ 4\ ]$

図7は操作5の故障定義操作のより詳細を示すフローチャートである。71は操作24で論理回路上に定義されているすべてのパス遅延故障について、信号経路上の設計上の遅延値の総和を算出する操作を示し、それ以外の記号は図2に一致する操作と同じものを示す。

#### [0065]

図8は操作7のテスト可否判定操作のより詳細を示すフローチャートである。 81は操作44で集計されたすべてのテスト不能故障について、信号経路上の設計上の遅延値の総和を算出する操作を示し、それ以外の記号は図4に一致する操作と同じものを示す。

#### [0066]

図9は操作8の故障検出率算出操作のより詳細を示すフローチャートである。 91は操作51の故障シミュレーションによって検出されたすべてのパス遅延故 障について、信号経路上の設計上の遅延値の総和を算出する操作を示し、それ以外の記号は図5に一致する操作と同じものを示す。

#### [0067]

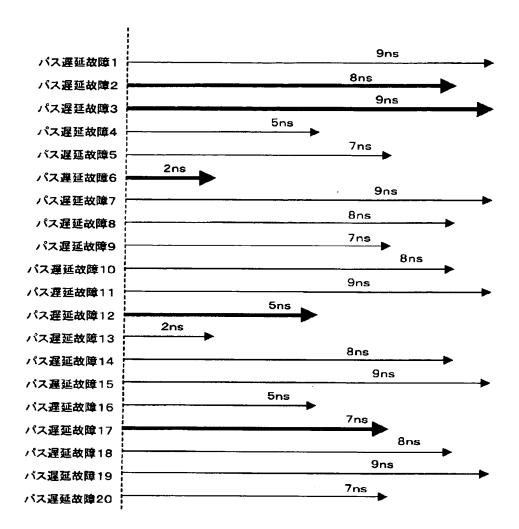

図10は、本発明に係わる遅延故障検査品質評価方法の動作を説明するための図である。パス遅延故障1~20は、論理回路データ1中に定義されるパス遅延故障を示し、各パス遅延故障の右側の矢印は各パス遅延故障が定義される信号経路の設計上の遅延値の大きさを示し、矢印の上の値はその具体的な遅延値を示す

#### [0068]

以下、図1、図3、図7~10を用いて本発明の第3の実施の形態を説明する

#### [0069]

初めに与えられた論理回路データ1に対して遅延故障定義情報2を用いて故障定義操作5を行う。遅延故障定義情報2には図10で示されている20個のパス遅延故障のリストが格納されている。次に故障定義操作5では、まず操作21において、遅延故障定義情報2で与えられたパス遅延故障を論理回路中の信号経路に定義する。ここで定義されたパス遅延故障数とその中に含まれるテスト不能故障数はそれぞれパス遅延故障2、10、15、20の4個であると仮定する。次に操作22では、定義した全パス遅延故障に対して簡易的なテスト不能パス判定を行い、その結果テスト不能と判定されたものが全くなかったとする。したがって次の操作23ではテスト不能と判定されたパス遅延故障が存在しないので何も行わない。次に操作24では、定義されている故障数が20個と集計される。最後に操作71では、定義されている20個のパス遅延故障について、信号経路の設計上の遅延値の総和を算出する。ここでは図10に示す各パス遅延故障の遅延値から、総和の値は141nsと算出される。

#### [0070]

次に部分故障選択操作6では、まず操作31でノードを1つ選択する。なお、 与えられた論理回路データ1中には3000のノードが存在するものとする。次 に操作32では選択したノードを通る定義されたパス遅延故障のうち、信号経路 上の遅延値が最も大きいパス遅延故障を選択する。もし選択したノードを通る定義されたパス遅延故障が存在しない場合は、そのノードは処理済みとして、操作33へ進む。今、選択されたパス遅延故障上に20個のノードが含まれたとする。引き続いて操作33では、未処理のノードがあるか否かの判定を行い、2980個のノードが未処理なので、再度操作31へ進み、未処理のノードを1つ選択し、操作32へ進む。今、選択したノードを通る定義されたパス遅延故障が存在しなかったとする。このとき、選択したノードを処理済として操作33へ進む。操作33では、未処理のノードがあるか否かの判定を行い、2979個のノードが未処理なので、再度操作31へ進む。同様に操作31から操作33の繰り返しを行い、判定33において未処理のノードが存在しなくなったら、最後に操作34において、これまで操作32で選択されたパス遅延故障を集計して故障リストを作成する。今、パス遅延故障2、3、6、12、17(図10において太線で示したパス遅延故障)の5個のパス遅延故障による故障リストが作成されたものとする。

# [0071]

次にテスト可否判定操作7では、まず操作41において、操作34で作成された故障リスト中のパス遅延故障2を選択する。次に操作42では、選択した故障に対する検査系列生成操作を行い、テスト不能と判定されたとする。引き続き操作43では、未処理の故障があるかどうかを判定する。ここではまだ4個の故障が残っているので、再度操作41へ進み、新たにパス遅延故障3を選択する。次に操作42では、選択した故障に対する検査系列生成操作を行い、テスト可能と判定されたとする。引き続き操作43では、未処理の故障があるかどうかを判定するが、まだ3個の故障が残っているので、再度操作41へ進む。同様に操作41から操作43を繰り返し、操作43において未処理の故障がなくなったら、操作44へ進み、操作42でテスト不能と判定された故障の数を集計する。今、操作42でテスト不能と判定された故障2のみの1個であったとする。最後に、操作81において、テスト不能と判定されたパス遅延故障2のみであるので、この遅延値8nsが総和として算出される。

# [0072]

次に故障検出率算出操作8では、まず操作51において、与えられた検査系列3を用いて故障シミュレーションを実施する。このとき対象となる故障は操作24で集計されたすべての故障である。この操作で検出された故障がパス遅延故障3、7、9、11、14、17、19の7個であったとする。次に操作91では、検出されたパス遅延故障の遅延値の総和を算出する。図10より総和の値は58nsと算出される。次に操作52では、操作91で算出された検出故障の遅延値の総和を検出故障量とし、操作24で集計された定義故障数を全定義故障数とし、操作71で集計された定義故障の遅延値の総和を全定義故障量とし、操作34で作成された故障リスト中の故障数を部分選択故障数とし、操作81で集計されたテスト不能故障の遅延値の総和を部分テスト不能故障量として、次の式によって全定義故障中のテスト不能故障推定量を算出する。

# [0073]

テスト不能故障推定量=部分テスト不能故障量

次に算出されたテスト不能故障推定量を用いて、次の式によって故障検出率を 算出する。

#### [0074]

故障検出率=検出故障量/(全定義故障量ーテスト不能故障推定量)

今、部分テスト不能故障量、全定義故障数、全定義故障量、部分選択故障数、 検出故障量は、それぞれ8 n s、20個、141 n s、5個、58 n s であるの で、(式4)よりテスト不能故障推定量は32 n s と算出され、次に(式5)に よって、故障検出率は53.2%と算出される。

#### [0075]

一方、実際のテスト不能故障(パス遅延故障 2 、 1 0 、 1 5 、 2 0 )の遅延値の総和をテスト不能故障量とすると、その値は 3 2 n s なので、実際の故障検出率を以下の式で算出すると 5 3 . 2 %となる。

#### [0076]

故障検出率=検出故障量/(全定義故障量-テスト不能故障量)

これに対して従来代用されていた(式 2 )による故障検出率ではテスト不能故障の数を全く考慮しないために 3 7. 7%となってしまい、与えられた検査系列による検査品質を誤って見積もってしまう結果となる。

#### [0077]

以上から、本発明による遅延故障検査品質評価方法では、テスト不能故障と推 定される故障の数を考慮することによって、実際の故障検出率に近い故障検出率 の値を算出することができる。

# [0078]

なお、部分故障選択操作6の実行方法として本実施の形態で説明に使用した図3の方法の代わりに、操作24で定義されている故障からランダムで所定数の故障を選択しても同様の効果が得られることは明らかである。

#### [0079]

また操作71、81、91では、パス遅延故障が定義された信号経路の設計上の遅延値を用いて説明を行っているが、信号経路の設計上の遅延値の代わりに、信号経路上のゲート段数か、または設計上の物理的な信号経路長を用いても同様の効果を得ることができる。なお、上記物理的な信号経路長はレイアウトデータから算出できる信号経路上の配線長の総和であってもよい。

#### [0080]

また同様に、操作32において、本実施の形態ではノードを通る最大遅延値のパス遅延故障を選択する、として説明を行ったが、最大遅延値の代わりに最大ゲート段数か、または物理的な最大信号経路長を用いても同様の効果を得ることができる。なお、上記物理的な信号経路長はレイアウトデータから算出できる信号経路上の配線長の総和を用いてもよい。

#### [0081]

#### 【発明の効果】

以上説明したように、本発明の遅延故障検査品質評価方法は、一部の故障に対してテスト不能故障を解析した結果を用いて、全定義故障中のテスト不能故障数

を推定することによって、実用的な計算量で精度の高い故障検出率を算出することができる。

# [0082]

また各遅延故障が定義された信号経路の設計上の遅延値を考慮することによって、個々の遅延故障の重要度を遅延故障検査系列の品質評価に反映させることができるため、遅延故障検査系列の品質評価の精度を高めることができる。さらに述べると、実際に故障を発生する可能性が大きい遅延故障ほど故障検出率への影響度合いを大きくすることができる。すなわち、そのような故障が検出された場合には故障検出率向上の度合いが大きく、逆に検出されない場合の故障検出率低下の度合いも大きくすることができる。

#### 【図面の簡単な説明】

#### 【図1】

本発明の実施形態に係わる遅延故障検査品質評価方法を示すフローチャート

# 【図2】

図1のフローチャートの一部をより詳細に説明するフローチャート

#### 【図3】

図1のフローチャートの一部をより詳細に説明するフローチャート

#### 【図4】

図1のフローチャートの一部をより詳細に説明するフローチャート

#### 【図5】

図1のフローチャートの一部をより詳細に説明するフローチャート

#### 図6

本発明の実施形態に係わる遅延故障検査品質評価方法を示すフローチャート

#### 【図7】

図1のフローチャートの一部をより詳細に説明するフローチャート

# 【図8】

図1のフローチャートの一部をより詳細に説明するフローチャート

#### 【図9】

図1のフローチャートの一部をより詳細に説明するフローチャート

# 【図10】

本発明の実施形態を補足する図

#### 【図11】

従来技術の課題を説明する図

# 【図12】

図2のフローチャートの一部をより詳細に説明するフローチャート

# 【図13】

図12の実施形態を補足する図

#### 【符号の説明】

- 6 部分故障を選択する操作

- 8 故障検出率を算出する操作

- 4 4 部分故障中のテスト不能故障数を集計する操作

- 52 故障検出率を計算する操作

- 62 部分故障を選択する操作

- 71 全定義故障の遅延値の総和を算出する操作

- 81 部分故障中のテスト不能故障の遅延値の総和を算出する操作

- 91 検出された故障の遅延値の総和を算出する操作

【書類名】 図面

【図1】

# 【図2】

# 【図3】

【図4】

【図5】

図6】

# 【図7】

【図8】

# [図9]

# 【図10】

【図11】

# 【図12】

【図13】

# 【書類名】 要約書

# 【要約】

【課題】 テスト不能な遅延故障をすべて算出するのが困難であることから、 遅延故障用の検査系列の故障検出率を算出する際に、テスト不能故障数を除外せ ずに故障検出率の算出を行っていなかったため、故障検出率がテスト品質を正し く反映していなかった。

【解決手段】 一部の遅延故障を選択して、選択された遅延故障中のテスト不能な遅延故障数を解析することにより、全体の遅延故障に含まれるテスト不能故障数を推定する。この値を用いてテスト品質を正しく反映した故障検出率の算出を行う遅延故障検査品質評価方法を提供する。

#### 【選択図】 図1

特願2003-021824

出 願 人 履 歴 情 報

識別番号

[000005821]

1. 変更年月日

1990年 8月28日

[変更理由]

新規登録

住 所

大阪府門真市大字門真1006番地

氏 名

松下電器産業株式会社